人工智能的快速发展正在引发数据中心的深入变革;计算密集型工作负载对CPU、加速器和存储之间的低延迟、高带宽连接提出了前所未有的高要求。Compute Express Link(CXL)互连技术为数据中心的性能和效率提升开辟了新的途径。

面对日益复杂的AI工作负载,数据中心各组件之间的高效通信变得至关重要。CXL通过提供低延迟、高带宽的连接来满足这一需求,从而提高整体内存和系统性能。

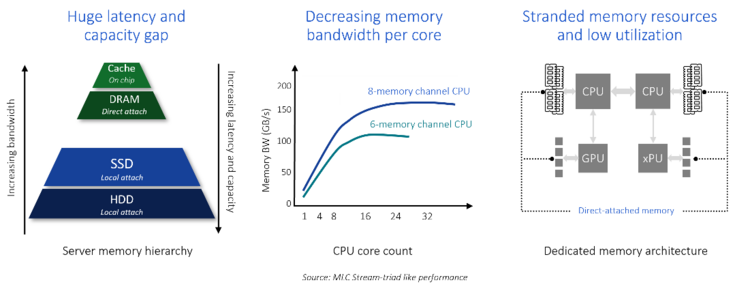

数据中心内存面临的挑战

CXL 3.1的数据传输速率高达64 GT/s并提供多层(网络连接)交换,可实现高度可扩展的内存池和共享。这些特色功能将成为下一代数据中心的关键,既能够减少高昂的内存成本和闲置的内存资源,又能够根据需要提供更高的内存带宽和容量。

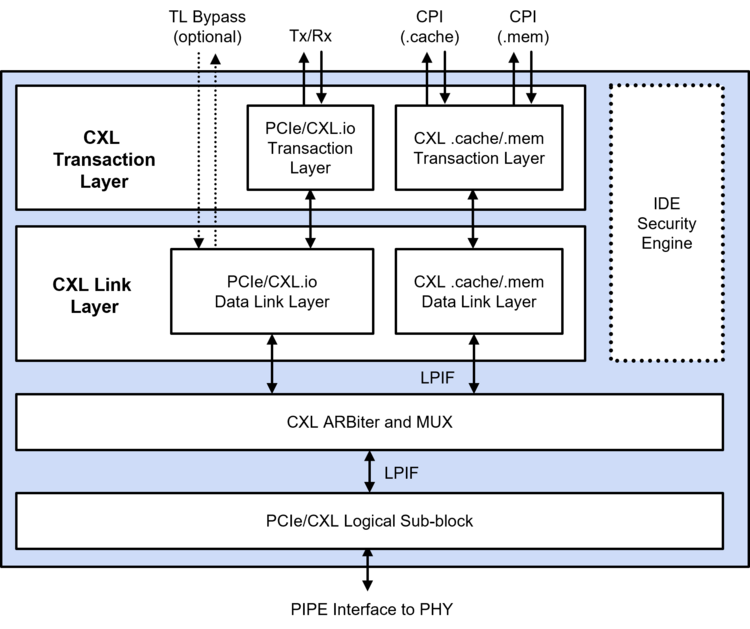

Rambus CXL 3.1控制器IP凭借灵活的设计,适用于ASIC和FPGA的实现。它采用适用于CXL.io协议的Rambus PCIe 6.1控制器架构,并且增加了CXL特有的CXL.cache和CXL.mem协议。内置的零延迟完整性和数据加密(IDE)模块可提供最先进的安全性,防止针对CXL和PCIe链路的物理攻击。这款控制器既可以单独交付,也可以与客户选择的CXL 3.1/PCIe 6.1 PHY集成。

CXL 3.1 控制器模块图

Rambus半导体IP总经理Neeraj Paliwal表示:“生成式AI和其他高工作负载的性能需求需要由CXL支持的新架构解决方案。Rambus CXL 3.1数字控制器IP扩大了我们在这一关键领域的领先地位,为我们客户的尖端芯片设计提供了CXL最新演进标准中的量、可扩展性和安全。

CXL是数据中心的关键互连技术,可应对数据密集型工作负载所带来的诸多挑战。与Lou Ternullo一起参加我们即将召开的网络研讨会“挖掘CXL 3.1和PCIe 6.1在下一代数据中心中的潜力”,了解CXL和PCIe互连技术如何帮助设计人员优化数据中心内存基础设施解决方案。

本文作者可以追加内容哦 !