台积电董事长暨总裁魏哲家亲口证实,公司已经开始研发FOPLP(扇出型面板级封装)技术,目前处于初始阶段,预计3年后准备就绪。这一宣告将加速FOPLP技术的发展,相关设备厂商也将迎来未来的大单。

设备业界普遍表示,对于大客户的加入及产业发展持“乐观其成”的态度,同时也会积极进行产品规格升级,以全面支持需求。据悉,台积电主要采用长宽各515毫米与510毫米的矩形基板,目前已有正式团队在进行研究,并规划建置mini line。

魏哲家简单分析称,FOPLP可以想象成矩形的Info,而台积电的规划是进一步整合3D Fabric平台上的其他技术,发展出类似矩形CoWoS-L的技术,主要针对AI GPU产品。

半导体业人士认为,早期FOPLP在台湾的主要玩家只有力成、群创、日月光,主要目的是提供具成本效益的封装方案,与台积电区隔开来。然而,技术发展却是走走停停,目前市面上仅有如PMIC这类成熟产品。

也正因此,过去设备商在相关领域的投资较为保守,目的是要将资源正确投放。然而,如今台积电正式宣告加入,加上封测厂在AMD、NVIDIA的号召下,也陆续重启投资,未来FOPLP的发展有望进一步拓展至游戏机、PC消费性市场领域,或是应用在AI GPU。

AI热潮正夯!而为发展如ChatGPT等大型语言模型(LLM),全球云端巨头无不广设资料中心,准妥「算力军火库」。然而,要打造具备生猛效能的AI晶片,先进封装就是个中关键!

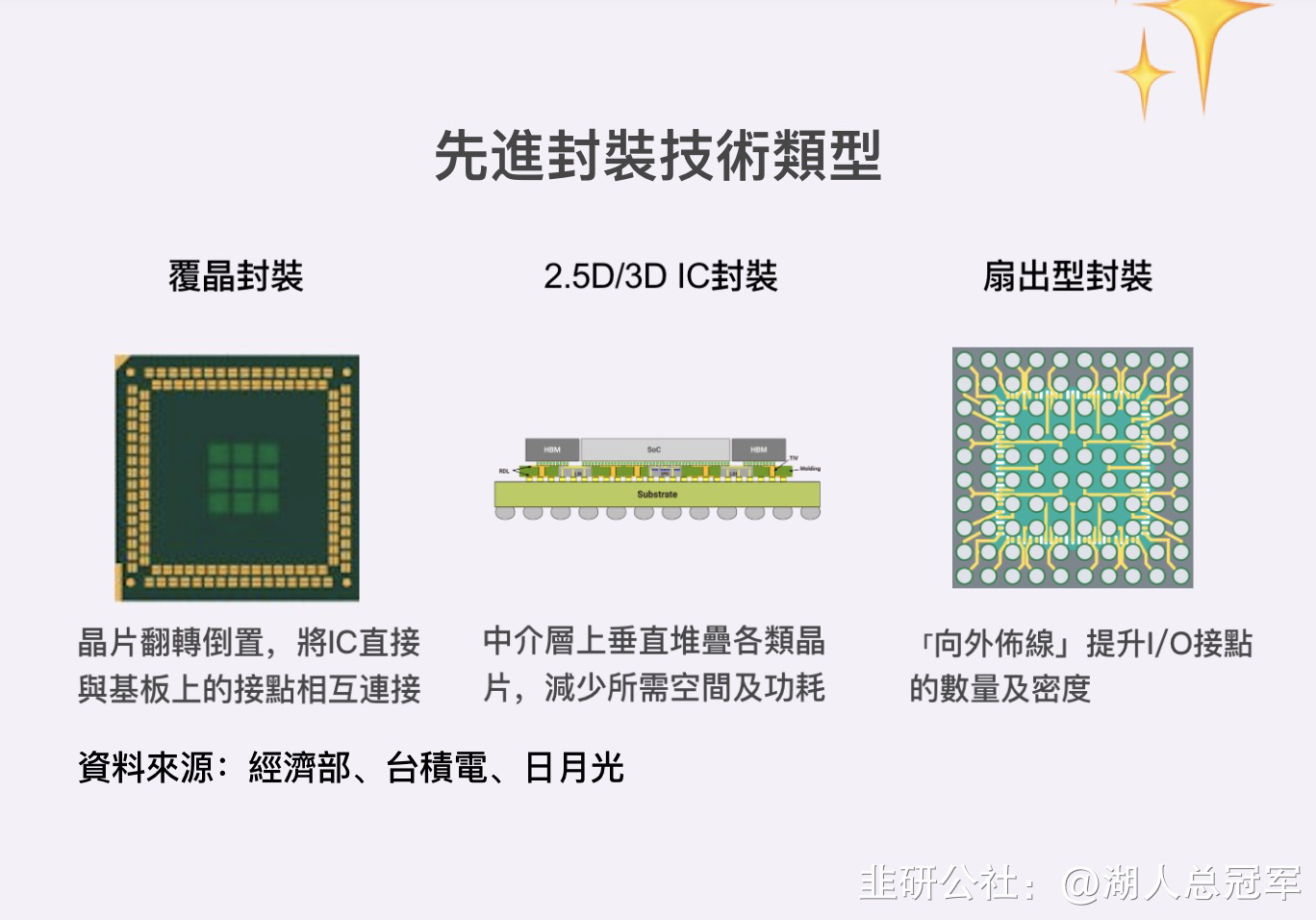

先进封装意味着将不同种类的晶片,包括逻辑晶片、记忆体、射频晶片等,透过封装及堆叠技术整合在一起,以提升晶片性能、缩小尺寸、减少功耗。例如,台积电针对7奈米制程以下的CoWoS技术,就是代表性的先进封装技术。

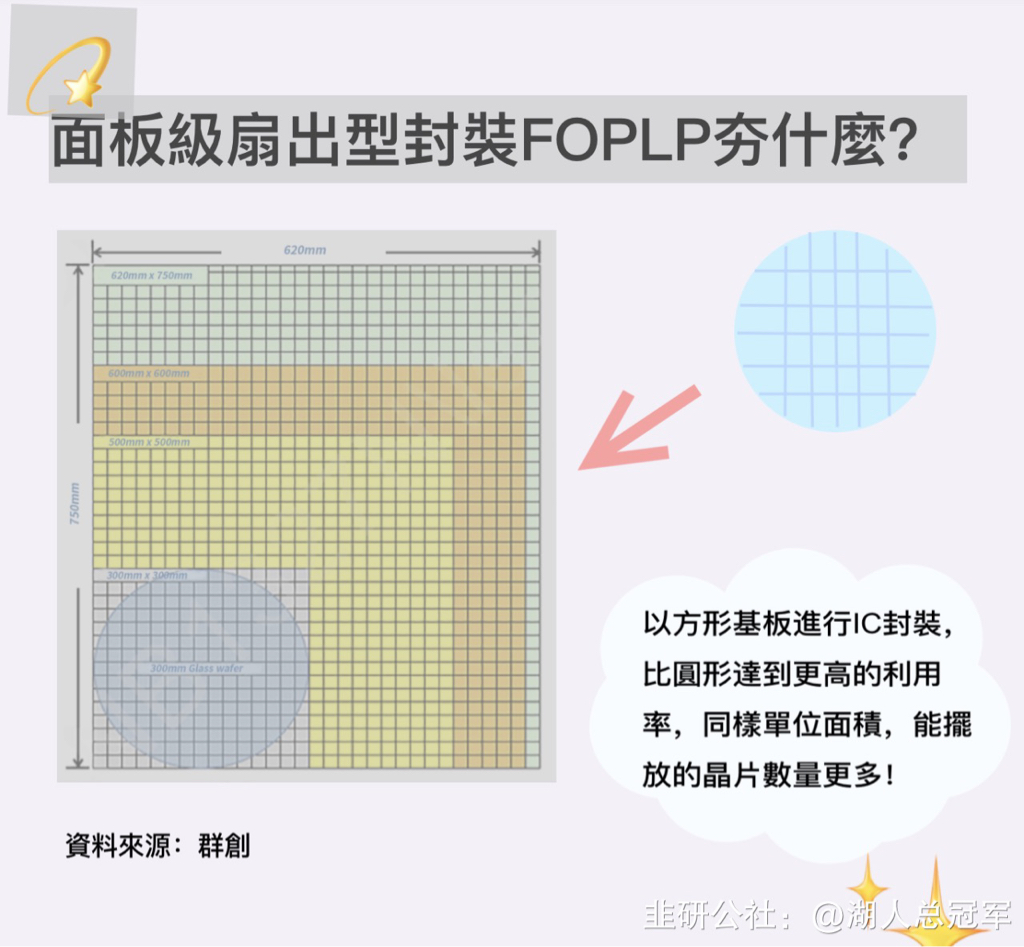

而FOPLP接棒台积电CoWoS备受关注的原因,在于透过「方形」基板进行IC封装,可使用面积可达「圆形」12吋晶圆的7倍之多,达到更高的利用率!白话来说,就是同样单位面积下,能摆放的晶片数量更多。

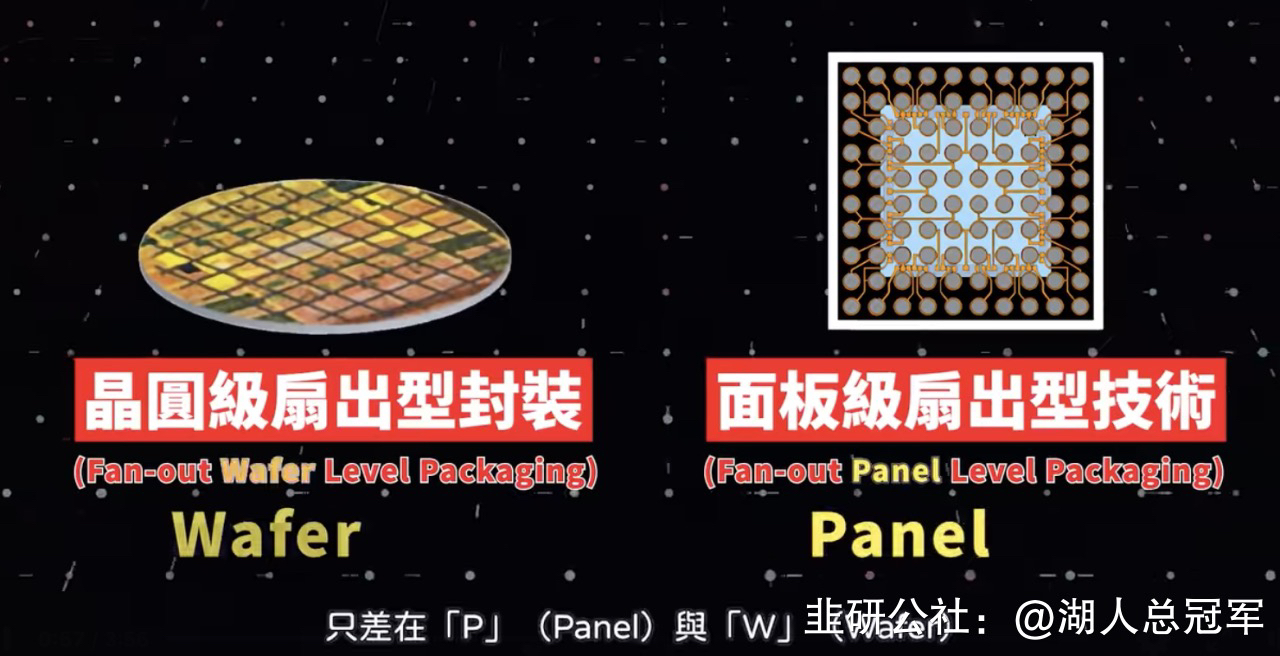

扇出型封装可再细分为两种分支,分别是已投入应用多年的扇出型「晶圆级」封装(Fan-Out Wafer-Level Packaging, FOWLP),以及本文主题的扇出型「面板级」封装(Fan-Out Panel-Level Packaging, FOPLP)。

扇出型晶圆级封装(FOWLP)和扇出型面板级封装(FOPLP)

「晶圆级」扇出封装的FOWLP,自2009年开始商业化量产,2016年,台积电率先将「整合扇出型」(Integrated Fan-Out, InFO)封装运用于苹果iPhone 7处理器,加速了高I/O数、功能强大的处理器采用FOWLP的趋势。

「面板级」的FOPLP则奠基于FOWLP基础, 将封装基板从圆形改为方形 ,如此在同样面积的基板上,能摆放更多的晶片,不仅生产效率提升,切割过程中浪费的材料也更少,成本相对降低。

面板级封装的优势主要在于成本。我们将300mm晶圆级封装与515x510mm面板级封装相比,可以看到如上图所示,面板级封装芯片占用面积比高到93%,而晶圆级封装则只有64%。这几何级别的差异,直接导致生产过程中生产速率UPH的巨大差异。

另外,根据Yole 报告,例如FOWLP技术面积使用率<85%,FOPLP面积使用率>95%,可以放置更多的芯片数,成本也比FOWLP便宜。具体推算从200mm过渡到300mm大约能节省25%的成本,从300mm过渡到板级,则能节约66%的成本。面板级封装的成本与晶圆级封装相比将会降低66%。

科翔股份:公司的面板级封装PLP工艺可以应用于3D封装相关产品。

本文作者可以追加内容哦 !