【前言】为什么要写公司深度文章,因为我们面对的投资噪音太多,经常只见树木不见森林,无法了解生意的本来面貌。我们立足于公开信息,客观理性分析,提出深度观点,还原生意本质。

FPGA厂商最初为何用门级数表示

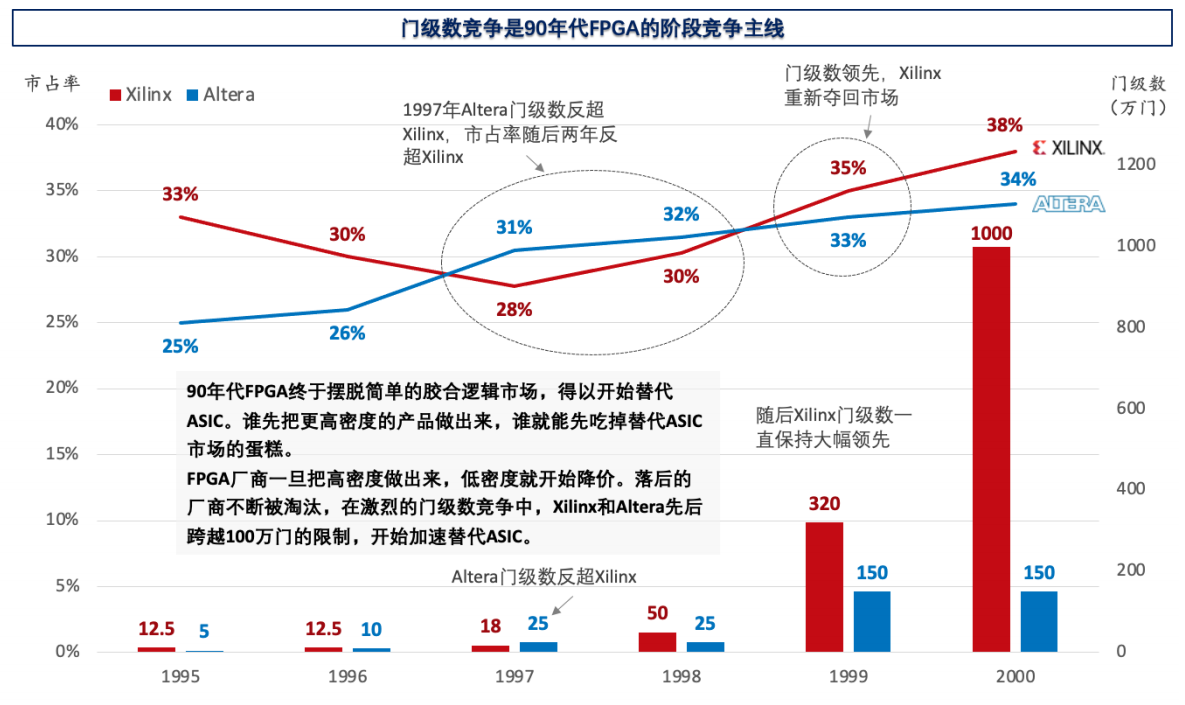

门级数竞争是 FPGA 厂商第一阶段的竞争主线(1985-2000)。替代 ASIC 的背后是性能提升的需求,门级数领先者往往获得大部分市场份额。

FPGA 诞生目的是为了替代门阵列等的 ASIC,ASIC 芯片的基本单元是与(AND)、或(OR)、非(INV)等基本逻辑门(Gate),其容量指标是门级数规模,出于这个考虑,90 年代初,FPGA厂商为更好的进行推广宣传,让客户更加了解 FPGA 芯片的性能,便为客户提供等效逻辑门数指标,方便与 ASIC 芯片进行对比。

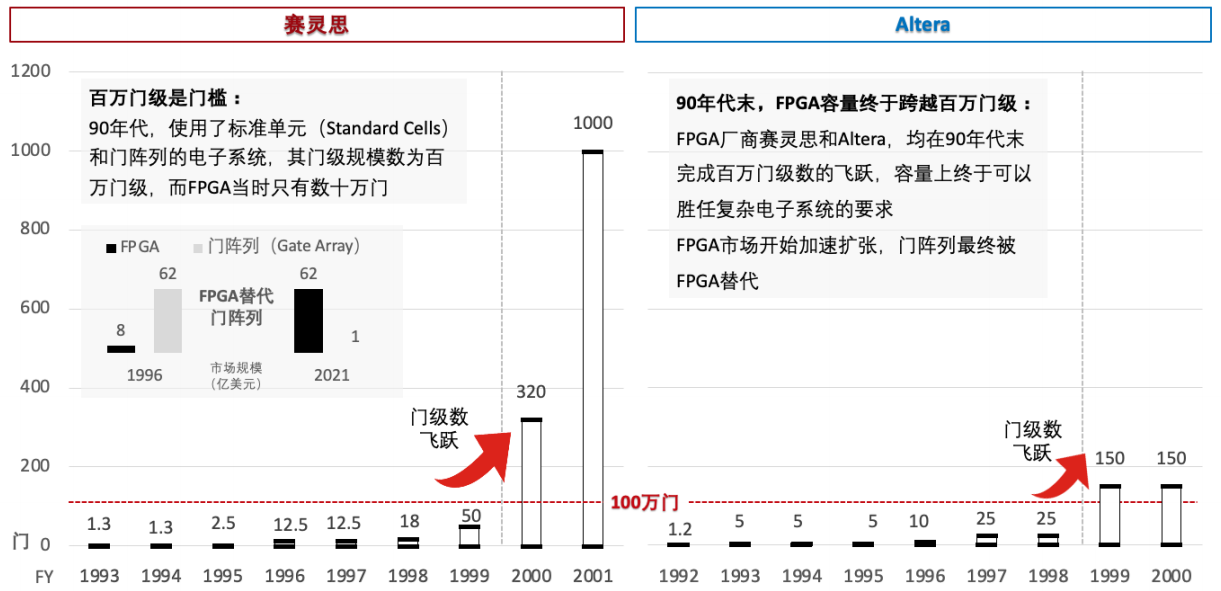

在当时,复杂的电子系统要求百万门级的规模,大多使用标准单元和门阵列实现,而 FPGA 当时容量只有 20-50 万门,无法进入高端市场。鉴于此,90 年代,FPGA 厂商纷纷在门级数上展开竞争,以拓展在高端市场的份额(谁先把更高密度的产品做出来,谁就能先吃掉替代 ASIC 市场的蛋糕)。门级数竞争也亦是 FPGA 厂商第一阶段的竞争主线。

通过 LUT 输入数量、簇结构、互联形式等的架构改善,辅之以摩尔定律的推动,FPGA 的密度和速度得以飞速提升。终于,Xilinx 和 Altera 先后在 1998-1999 年跨越 100 万门的限制,FPGA 开始加速替代门阵列、标准单元和 ASIC,市占率得到持续的提升。(FPGA 厂商一旦把更高密度的产品做出来,低密度就开始大幅降价,落后的厂商不断被淘汰)

此时,FPGA 的门级数已经可以比肩门阵列等竞品,没有必要再将逻辑资源数转化为门级数了。

同时,随着 FPGA 集成度的提升,不断将 RAM、DSP、CPU 等功能嵌入到 FPGA 中,以及 LUT4 逐渐提升到 LUT6、LUT8 甚至更高,将 FPGA 的容量转化为门级规模数越来越困难(FPGA 芯片的基本逻辑电路单元是查找表(LUT),LUT 单元如何等效转换为逻辑门,在工业界和学术界没有统一的计算方法;FPGA芯片上的整块 RAM 存储单元、整块 DSP 运算单元、高速接口等资源也无法准确地换算为等效逻辑门数)。

由于计算方法缺乏统一标准,在 2000 年后,国际上越来越多使用“逻辑单元数”作为基本容量指标,因其能更好代表 FPGA 可调用的资源数,赛灵思从 2005 年之后不再提供门级数规模,而是改用逻辑单元数这一指标。

总结:过去,FPGA 厂商曾经使用门级数规模来衡量 FPGA 的容量,但从 2000 年后就逐渐转用统一的“逻辑单元数”指标了,这是因为:1)门级规模数是 FPGA 容量的间接指标,逻辑单元数量才是 FPGA 容量的直接指标,90 年代末,FPGA 在门级规模数上比肩门阵列等竞品,没必要再转换为竞品的评价指标了;2)随着 FPGA 集成度的提升,不断将 RAM、DSP、CPU 等功能嵌入到 FPGA 中,以及 LUT4逐渐提升到 LUT6、LUT8 甚至更高,将 FPGA 的容量转化为门级规模数越来越困难。

计算方式

门数计算方式:

在常用的 CMOS 集成电路工艺中,通常用四个晶体管实现一个 2 输入的与非门。这样也基本可以粗略的认为在传统 CMOS 工艺中 4 个晶体管为一个门。如:该集成电路千万门,也就意味着如果把这个集成电路所用的晶体管除 4,基本就是该电路的门数。

FPGA 说多少万门的概念,最早是 Xilinx 公司按业界的传统数字集成电路定义方法来定义自己产品的规模,也就是说该款产品内部所用的单元电路能够折算成多少 2 输入与非门。

门数转换方式:

把 FPGA 基本单元(如 LUT FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该 FPGA 基本单元的等效门数,然后乘以基本单元的数目就可以得到 FPGA 的等效门数估计值。

门级指标:

目前门级规模在 FPGA 中常作为判断其性能的指标之一,代表着 FPGA 可开发的潜力,门级规模越大,用户在使用 FPGA 时,可以开发更多功能,解决更多问题。

风险提示:本内容仅代表破卷研究的分析、推测与判断,登载于此仅出于传递信息之目的,不作为投资具体标的之依据。投资有风险,入市需谨慎!

版权声明:本内容版权归原创方或原作者所有,如转载使用,请注明来源及作者、文内保留标题原题以及文章内容完整性,并自负版权等法律责任。

$复旦微电(SH688385)$

本文作者可以追加内容哦 !