【前言】为什么要写公司深度文章,因为我们面对的投资噪音太多,经常只见树木不见森林,无法了解生意的本来面貌。我们立足于公开信息,客观理性分析,提出深度观点,还原生意本质。

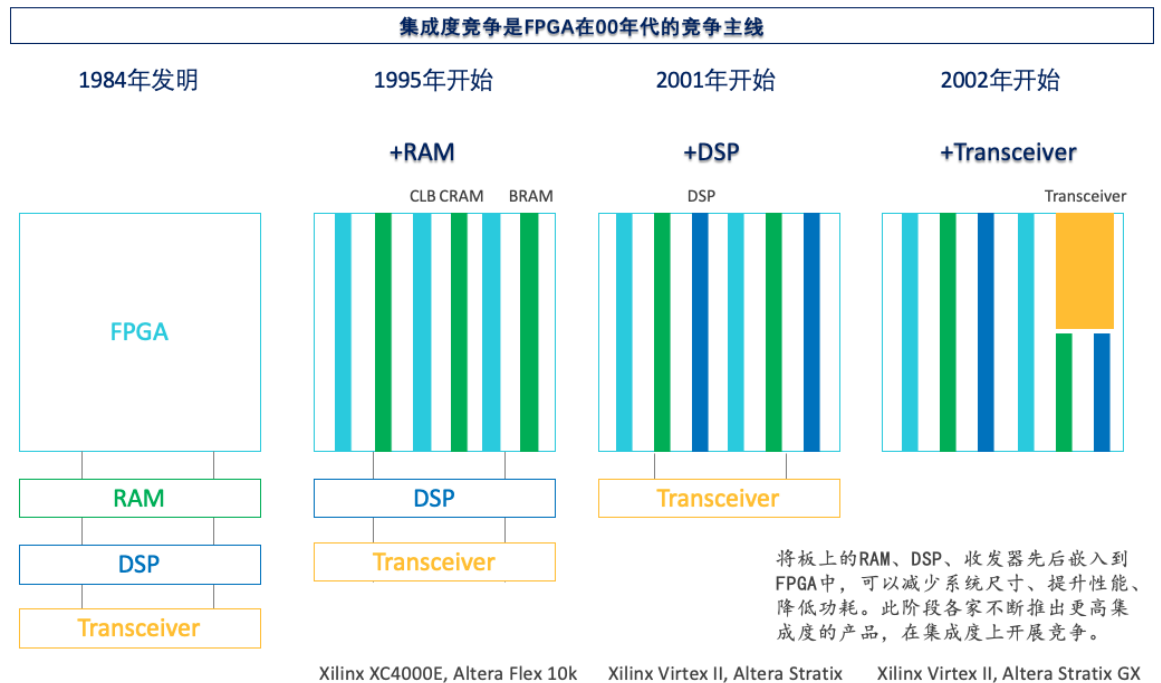

集成度竞争

以 BRAM(块随机存取存储器)、DSP(数字信号处理器)、收发器等为代表的固化单元性能是 FPGA 性能体系的第二大部分。除了可编程的逻辑单元外,现代的 FPGA 还集成了许多固化单元,常说的 FPGA 的 SerDes 速率、DSP 工作频率等,都是在谈论 FPGA 中不同的固化单元的性能。

集成度竞争是 FPGA 厂商第二阶段的竞争主线 (2000-2010)。将板上分立的 DSP 等器件纳入到FPGA,背后是减少电路面积、降低功耗和系统成本的需求,先推出高集成度 FPGA 的厂商获得了更多的替代 DSP 等竞争产品的份额。

90 年代中期,FPGA 厂商发现用户在使用 FPGA 时,会频繁将 LUT 作为存储使用(即“软”实现),占用了许多逻辑单元,导致 FPGA 容量出现不够的情况。因此,RAM 是第一个被固化到 FPGA 中的单元,即“硬核”化。

将这些用户频繁使用到的功能固化到 FPGA 中,可以极大地提升计算效率,用户也不需要为浪费宝贵的逻辑资源而烦恼,而且可以减少板上的走线、管脚和焊盘,进而减少 PCB 板的面积和功耗。例如,将 DSP 嵌入到 FPGA 中(而不是通过万能的 LUT 实现),可以节省 80% 的功耗和 DSP 在板上占用的面积。

因此,在 90 年代末完成门级数的超越后,FPGA 厂商的竞争主线从门级数转向集成度竞争,先后将原本属于板上的 RAM、DSP、收发器、DDR 接口、CPU、GPU 等单元嵌入到 FPGA 中,以降低客户的功耗和总系统成本,并进一步蚕食板上其它分立器件的市场,这是现代的 FPGA 中往往包含了许多固化单元的原因。因此,从 FPGA 的性能评价指标上,也往往涉及到这些固化单元。

*Altera 的 FLEX 10K 是第一个嵌入了 RAM 的 FPGA,Xilinx 在 00 年通过收购 Rocketchip 拥有了高速收发器能力,并在 02 年 3 月发布的 Virtex II Pro 中嵌入了收发器。

其他容量及性能技术指标

FPGA 芯片的技术水平主要体现在容量和性能两个方面。LUT 数量是 FPGA 芯片容量的基础性指标。性能方面,工艺制程直接影响芯片的功耗和性能,门级规模代表着 FPGA 可开发的潜力,这三个重要指标在前面文章已做详细分析,另外还有例如 SerDes 速率、DSP工作频率等技术指标,具体介绍如下:

DSP 数量:FPGA 芯片数字信号处理能力的重要指标。DSP 单元可以实现多个数的乘法、加减法、宽位逻辑操作等功能。DSP 的主要参数包括乘法器的位数和加法器的位数。

DSP 工作频率:DSP工作频率越高,数据运算速度越快。通常以兆赫兹(MHz)为单位。

RAM 容量:FPGA 芯片中数据存储能力的重要指标。RAM 包括多个内嵌整块 RAM 和用 LUT 实现的分布式 RAM。RAM 的存储容量通常以 Kbit 为单位。

User IO 数量:FPGA 芯片数据接口能力的重要指标。指用户可用的最大输入/输出接口数量。

SerDes 速率:FPGA 的 SerDes 速率直接反映了 FPGA 与外界联通的能力。步入信息社会,数字信息的爆发导致了硬件承载数据量的爆炸式增长,在提高设备系统数据处理能力的同时,还需要提高其数据传输能力,避免大量数据等待处理而导致数据拥塞。该速率越高,数据传输量越大。通常以 Gbps 为单位。

在 5G 时代,SerDes 需要达到 28Gbps 甚至更高的 32Gbps,才能满足 5G 通信协议的“肚量”,而进入人工智能时代,大量的、重复的数据传输甚至将超出 32Gbps 的传输能力范围,从而要求 FPGA 达到 56Gbps 甚至更高的传输速率。

DDR 速率:指 DDR2/DDR3/DDR4/DDR5 同步动态随机存储器数据读取接口的标准速率。数据速率单位以 MT/s 为单位。

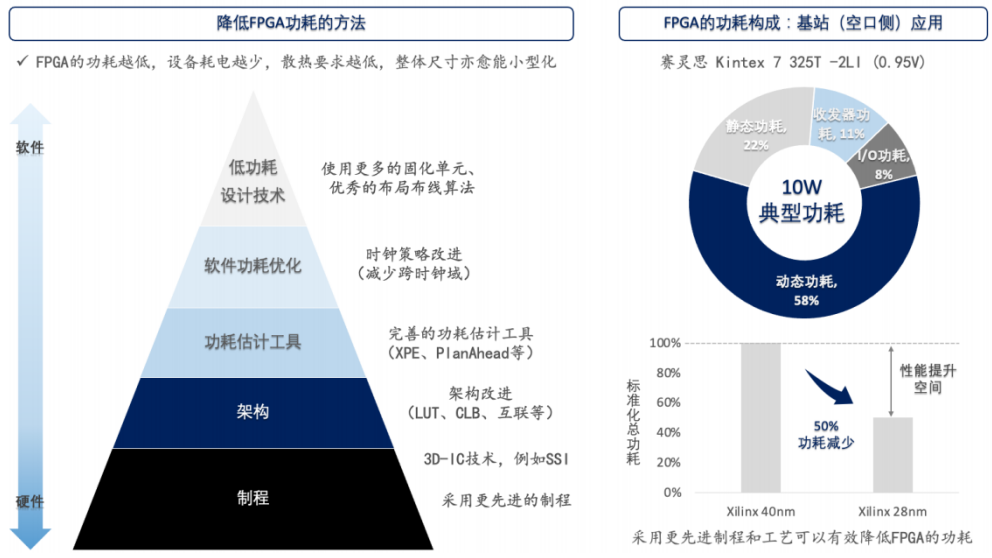

功耗:FPGA 的总功耗由静态功耗、动态功耗、IO 功耗和收发器构成,静态功耗是电路的功耗,主要是由晶体管漏电造成;动态功耗指芯片处于工作状态时电路翻转产生的功耗,来源于时钟、逻辑、BRAM、处理单元、收发器等单元,动态功耗越低,芯片耗电越少。芯片功耗越低,芯片寿命越长,设备的耗电就越少,散热要求越低(或不需要额外的散热改造),整体尺寸亦愈能小型化。一般来说,嵌入式处理非常看重功耗,功耗预算不超过 50W。FPGA公司通过两种方式降低功耗:1)硬件上,使用更先进的制程和工艺、3D-IC 技术、嵌入更多的固化单元、更低功耗的架构;2)软件上,优化布局算法,以减少跨时钟域和多余的逻辑资源的占用,以及提供功耗估计工具方便用户修改。

因此,不少厂商在功耗上另辟蹊径,以建立在低容量市场的竞争优势,从而摆脱低容量市场单纯依靠量大低成本的竞争方式,以及一贯以来的价格战问题。低容量市场技术成熟,进入壁垒相对较低,厂商之间提供的产品差异不大,往往容易出现价格战的问题。但由于“性能-功耗-便携性”的矛盾一直存在,低容量市场对低功耗的追求同样在不断增长。因此,优化功耗的能力是低容量市场厂商除了价格之外的的竞争法宝。

*例如,目前全球出货量最高的 FPGA 厂商 Lattice,其 Certus 系列就使用了 FD-SOI工艺,比起基于 CMOS 的竞品,例如 Altera 的 Cyclone、赛灵思的 Artix,其功耗要低 70%-75%。因此,尽管 Lattice 在 FPGA 全球市占率仅为 5%,没有大容量 FPGA 产品线,但凭借在功耗上的优势,在低容量市场优势明显,整体毛利率同样能达到 50%以上。

*该篇文章篇幅过长,国内厂商主要产品的技术指标情况放于后续文章中分析总结

风险提示:本内容仅代表破卷研究的分析、推测与判断,登载于此仅出于传递信息之目的,不作为投资具体标的之依据。投资有风险,入市需谨慎!

版权声明:本内容版权归原创方或原作者所有,如转载使用,请注明来源及作者、文内保留标题原题以及文章内容完整性,并自负版权等法律责任。

$复旦微电(SH688385)$

本文作者可以追加内容哦 !