【前言】为什么要写公司深度文章,因为我们面对的投资噪音太多,经常只见树木不见森林,无法了解生意的本来面貌。我们立足于公开信息,客观理性分析,提出深度观点,还原生意本质。

为什么 FPGA 厂商要有自己的 EDA 软件

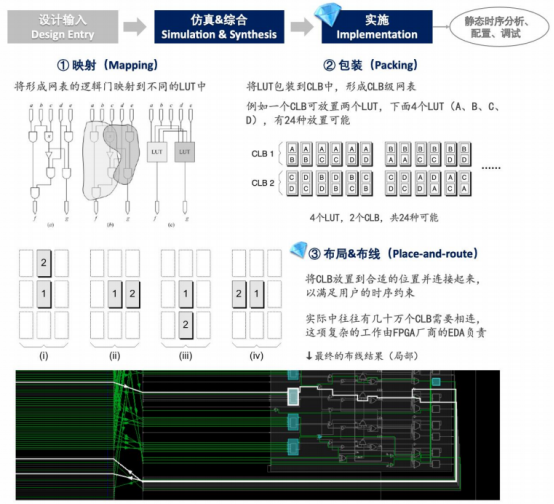

将目标电路在 FPGA 上实现,包含了三个最核心的步骤:1)映射(Mapping):将电路的逻辑门映射到不同的 LUT 中,形成 LUT 级网表;2)包装(Packing):将这些 LUT 放置到 CLB 中,形成 CLB 级网表;3)布局&布线(Place-and-route):将 CLB 放置在合适的位置并彼此相连。由于数据信号的处理和传输需要时间,时钟信号的传递和变化也需要时间,如果布局和连线的方式不合理,就会出现数据到达下一个寄存器的时间过晚或者过早,即数据采集失败的情况。

大型的电路往往有数十万个 CLB 需要相连,这项复杂的工作由 FPGA 厂商的 EDA 工具负责,例如赛灵思的 Vivado,Altera 的 Quartus,这些 EDA 将电路映射到多个 CLB 上,并且找到合理的布局和连接方式,确保电路能在用户指定的频率上工作,即满足时序约束。因此,连线的可编程性更多地体现在 EDA 软件对于时序约束的满足能力上。如何提高自家 EDA 在映射、包装、布局&布线这三个核心步骤的效率,以减少客户的设计用时(进而培养使用习惯),一直都是 FPGA 公司的研发重点,也是其竞争法宝。

布局布线是 FPGA 厂商的独门秘籍,是其 EDA 的核心。完整的 FPGA 设计流程包括三大步骤:设计输入(Design Entry)、仿真&综合(Simulation & Synthesis)、实施(Implementation)。“设计输入”指将电路用硬件描述语言(Verilog 或 VHDL)描述,“仿真”即检查描述的电路功能是否完整,“综合”负责电路的映射和包装,“实施”即布局&布线。在随后的静态时序分析(STA)和调试无误后,形成比特流文件下载到 FPGA 中,电路就可以“跑”起来了。尽管 FPGA 厂商的 EDA 工具能提供一套完整的流程,但在设计大型电路时,电路的验证仿真往往交给第三方的 EDA 完成,例如 Mentor 的 ModelSim。而 FPGA 的 EDA 则负责进行下一步的综合(甚至综合也可以在第三方 EDA 中完成,例如 Synopsys 的 Synplify)。这是由于电路仿真不涉及 FPGA 的具体架构,只需考虑电路功能的完整性。随着电路的大型化和复杂化,这一工作逐渐由第三方EDA 公司承担。而 FPGA 厂商的 EDA 真正核心之处在于布局和布线。因为布局布线涉及 FPGA 的内部具体架构,这是每家 FPGA 公司的机密,无法交给第三方完成,这是 FPGA 厂商需要自研 EDA 的根本原因。从 FPGA 诞生以来,布局布线就从来只在 FPGA 公司的 EDA 上进行。

EDA 的竞争因素考量

FPGA 硬件和设计工具绑定的特点,使得 EDA 和硬件必须做到并重开发。FPGA 的 EDA 有两个方面的竞争因素考量:1)软件的易用性;2)核心的“映射-包装-布局布线”算法。前者可以稍落后于硬件,而后者是和硬件的架构高度绑定的,必须与硬件同时发展。虽然仿真等工作可以由第三方 EDA完成,但由于架构不公开,并不存在通用的 FPGA 布局布线工具,布局布线只能由 FPGA 厂商自己的 EDA软件完成。因此,FPGA 的容量每上一个台阶,就必须更新配套的“映射-包装-布局布线”三大算法。历史上有过通用的 FPGA 全流程 EDA 开发尝试,但都无一例外失败了。对于客户来说,切换 FPGA 厂商不仅仅是适应新的开发环境所花费的时间和经历,其设计在 FPGA 上实现的效率亦各不相同。而且开发软件是以免费或者非常低的价格提供给购买了 FPGA 的用户的,软件本身不产生收入。这种硬件和软件高绑定的特点,使得 FPGA 新进厂商在攻克了硬件的诸多技术难点外,还要完成配套软件的开发,这是 FPGA 的设计难于其它类型芯片的原因,亦是 FPGA 的进入壁垒如此之高的原因之一。历史上赛灵思和 Altera 都曾与第三方的 EDA,比如 Synopsys、Mentor 合作优化仿真以及综合的流程,但布局布线从来只在自己的 EDA 上进行。

*EDA 篇幅由于过长,分为上下两篇,该篇描述 EDA 的重要性及竞争因素考量,有一个大概了解,下篇会阐述复旦微电 EDA 软件技术。

风险提示:本内容仅代表破卷研究的分析、推测与判断,登载于此仅出于传递信息之目的,不作为投资具体标的之依据。投资有风险,入市需谨慎!

版权声明:本内容版权归原创方或原作者所有,如转载使用,请注明来源及作者、文内保留标题原题以及文章内容完整性,并自负版权等法律责任。

本文作者可以追加内容哦 !