【前言】为什么要写公司深度文章,因为我们面对的投资噪音太多,经常只见树木不见森林,无法了解生意的本来面貌。我们立足于公开信息,客观理性分析,提出深度观点,还原生意本质。

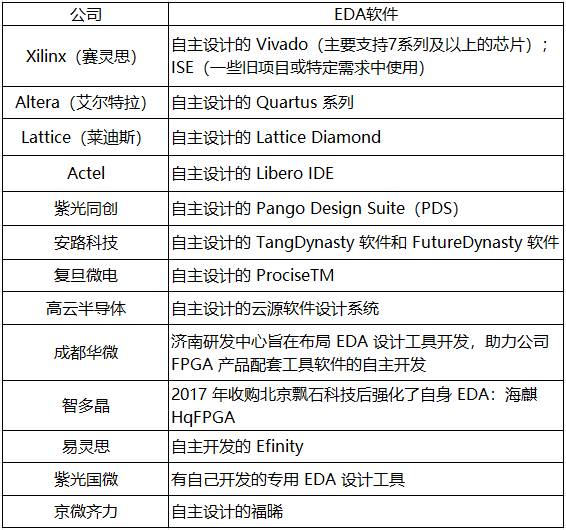

主要 FPGA 厂商的 EDA 概览

主要 FPGA 厂商基本均有自主开发设计的 EDA 软件来作配套,具体如下:

复旦微电 FPGA 配套 EDA 软件相关技术

Procise 是一款由复旦微自主研发设计的致力于完整可编程器件开发流程的工具软件,主要包括网表导入、映射装箱、布局布线、时序分析与优化、位流生成、编程下载、在线调试等功能。该配套开发软件集成了以下关键技术:

Procise 软件的主要特点有:国产自主研发的致力于完整 FPGA 开发流程的 EDA 软件;内嵌时序分析工具,实现设计、验证一体化,提高效率;优异的下载配置性能,速度较同类软件更快;支持多样化的在线调试功能,缩短设计周期;界面简洁友好、易使用;

一种 FPGA 总体布局合法化方法:该技术通过分级处理不同类型不同约束的单元模块的合法化,确保总体布局的有效性,减少合法化对总体布局的破坏;

一种 FPGA 详细布局的模拟退火方法:在优化布局质量与速度、增强多目标优化能力、提升 FPGA 设计的灵活性与可靠性等方面具有显著的技术作用;

一种基于解析方法的总体 FPGA 自动化布局方法:在提高布局效率与自动化水平、优化布局质量、提升设计灵活性和降低设计成本等方面具有显著的技术作用;

可编程逻辑器件的 I/O 单元布局方法及装置、介质及设备:提高了布局效率和布局质量,还提升了设计灵活性和降低了设计成本;

一种基于查找表的 FPGA 芯片逻辑单元时延建模方法和系统:提高了时序分析的准确性和效率、支持复杂逻辑设计、优化布局布线并推动 FPGA 技术创新和发展;

一种 FPGA 芯片版图连线显示方法:该 FPGA 芯片版图连线显示方法支持放大缩小,元器件、元器件之间连线、可编程连接点等元素的高亮显示并可提高查询速度,减少内存使用;

FPGA 的装箱方法及设备:该方法将多个逻辑单元装入物理单元中,从而实现逻辑网表到物理网表的转换,使物理网表可以直接在 FPGA 器件上实现该实现方法上具有灵活性和可扩展性,从而能够均衡地或有偏向性地考虑各个约束和优化目标;

时延评估方法及装置、可读存储介质:该时延评估方法当接收到线网连接信息时,从预设的路径表中查找对应的时延估计信息;基于查找到的时延估计信息,得到时延评估结果并输出应用该方法,可以提高时延评估的速度及准确性。

另外,公司与新一代 FPGA 平台开发及产业化项目产品配套工具 VultureTM EDA 软件也正在内部测试中。具体来说,该工具的开发工作已经取得了显著进展,部分功能已经得到验证,预计下半年首次发布。

风险提示:本内容仅代表破卷研究的分析、推测与判断,登载于此仅出于传递信息之目的,不作为投资具体标的之依据。投资有风险,入市需谨慎!

版权声明:本内容版权归原创方或原作者所有,如转载使用,请注明来源及作者、文内保留标题原题以及文章内容完整性,并自负版权等法律责任。

$复旦微电(SH688385)$

本文作者可以追加内容哦 !