摘要

NSIP8xxx系列是纳芯微推出的国内首款内置片上变压器,集成隔离DC-DC电源的数字隔离芯片,实现在宽体SOW16的封装内集成3.3V/5V输入,3.3V/5V输出可选的DC-DC转换模块,外加4个数字隔离通道,为系统的小型化和简化生产提供了便利。

为了实现片内集成小型变压器,必须提高电源开关频率,带来的主要困扰便是辐射问题。NSIP8xxx系列通过内部电路设计减少芯片辐射噪声,只需要外部简单的PCB设计即可实现CISPR32 CLASS B的标准。

1. EMI的产生原因

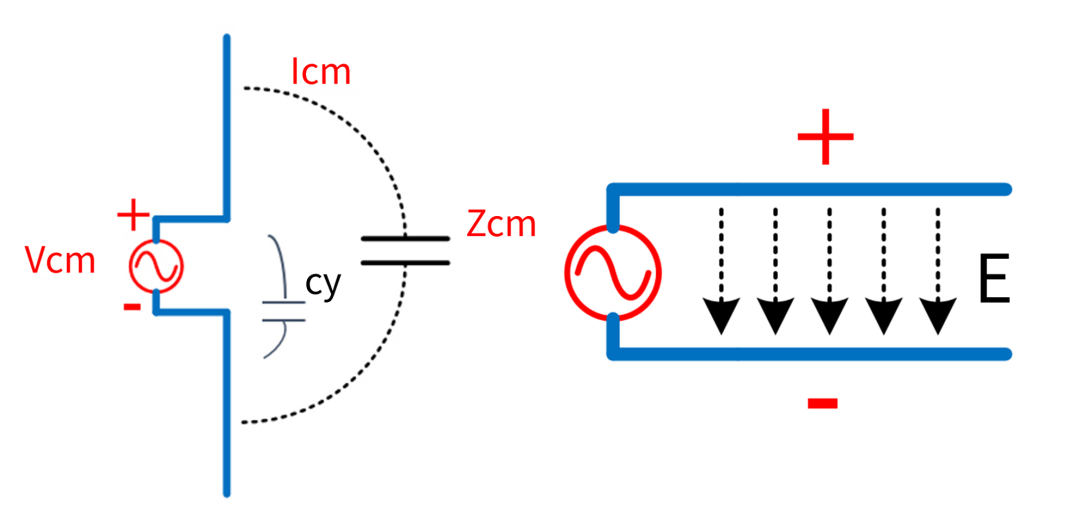

隔离电源模块产生的辐射主要为共模辐射,即小型变压器的寄生电容带来的偶极子辐射。隔离电源芯片正常工作时,变压器原边的共模电压与变压器副边的共模电压之差是在高频变化的,高频变化的共模电压差通过原副边线圈间的寄生电容形成电流。该电流从原边流到副边或从副边流到原边后,没有返回路径,只能通过天线向外辐射,即产生共模辐射。共模辐射的模型如图1.1所示:

图1.1 共模辐射模型

其中:

• Vcm为原副边电源(地)之间的共模电压差(对于高频交流噪声而言,电源和地是同一电位)。

• Icm指流入天线,进行辐射的电流。

• 双边天线主要是隔离的原副边地(因为地线一般较长)。

2. 降低EMI的方法

针对以上EMI产生原因,降低共模噪声EMI主要有以下途径:

2.1 在原副边之间使用PCB产生拼接电容

将耦合到副边的噪声通过电容旁路回原边的大地,可以减少传输线上的共模干扰电流。

由于安规电容引脚的寄生电感及其自身的感性,会使得拼接电容阻抗较大,耦合到副边的噪声通过电容旁路回原边大地的效果很差,所以不建议使用安规电容。

使用PCB两层金属平面交叠时,可以产生拼接电容。该类拼接电容具有寄生电感低的优点。

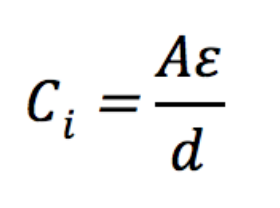

以4层PCB为例,由于表层有安全间隙要求,因此选用第二层和第三层形成拼接电容。相对于高频交流噪声而言,同侧电源和地的电位相同,所以用于产生拼接电容的延伸的PCB金属平面既可以是电源层,也可以是地层。以第二层电源层和第三层地层为例,产生的拼接电容如图2.1所示。

图2.1 拼接电容产生原理示意

原副边延伸的PCB金属平面产生的等效电容值的表达式:

其中:

• =0r,0为自由空间的介电常数8.854pF/m,r为PCB绝缘材料的相对介电常数(FR4材质约为4.2)。

• Ci为拼接电容的容值。

• A为延伸PCB的交叠面积。

• d为地平面和电源平面的绝缘材料厚度。

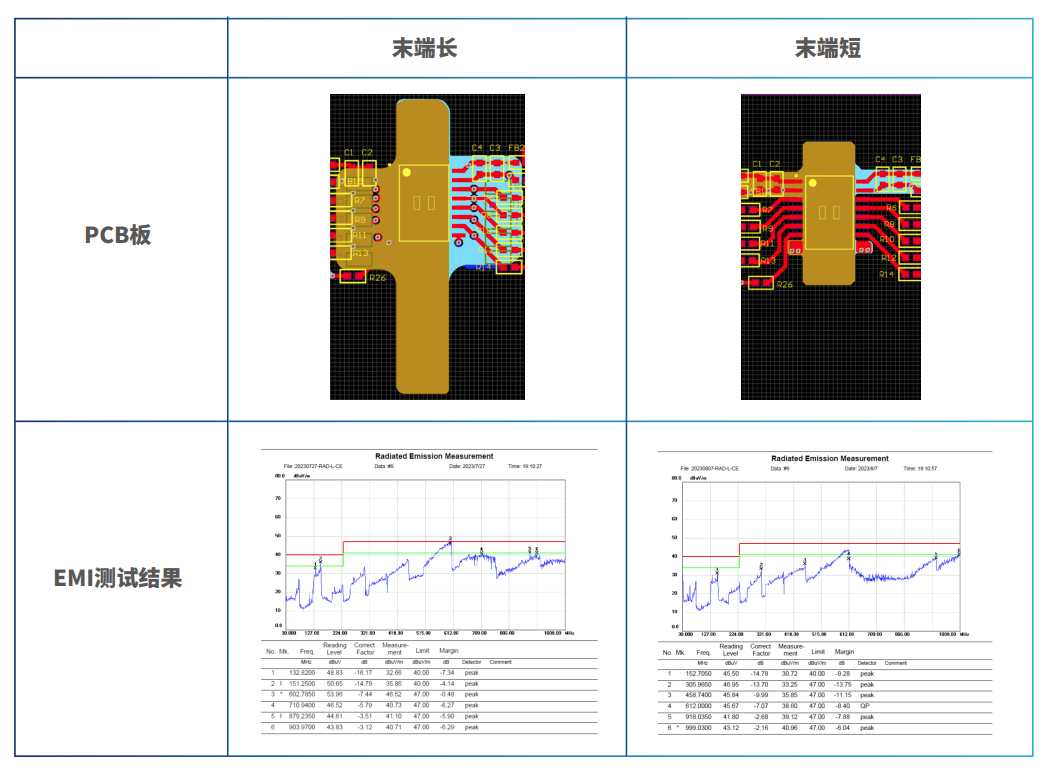

注意,拼接电容到芯片pin脚的走线上也存在寄生电感,所以产生拼接电容的金属平面末端到芯片pin脚的走线距离不应过长,否则拼接电容的天线效应会比导流效应更强,使得共模辐射增大。在其他条件均相同,但拼接电容金属平面末端到芯片pin脚距离不同的情况下,测试结果如表2.1。测试条件为输入电压5V,输出电压5V,输出电流100mA。

表2.1 拼接电容末端长度对EMI结果的影响

(未完持续)

长按扫描下方二维码,

免费下载完整应用笔记。

纳芯微电子(简称纳芯微,科创板股票代码688052)是高性能高可靠性模拟及混合信号芯片公司。自2013年成立以来,公司聚焦传感器、信号链、电源管理三大方向,为汽车、工业、信息通讯及消费电子等领域提供丰富的半导体产品及解决方案。

纳芯微以『“感知”“驱动”未来,共建绿色、智能、互联互通的“芯”世界』为使命,致力于为数字世界和现实世界的连接提供芯片级解决方案。

了解详情及样片申请,请访问公司官网:

www.novosns.com