闷得而蜜

发布于2024-11-03 11:19来自雪球 · 广东

光进铜退,极限在哪里

来自闷得而蜜的雪球专栏

英伟达的Blackwell GB200 NVL72迟迟不能量产,台积电大肆宣传它的COUPE硅光平台后,台湾硅光产业联盟高调成立,国内多个省份先后发布光电子先进生产力产业规划,光进铜退的理念越来越深入人心。那么光进铜退的纵深在哪里呢?终极目标在哪里呢? 本文主要回答这个问题。

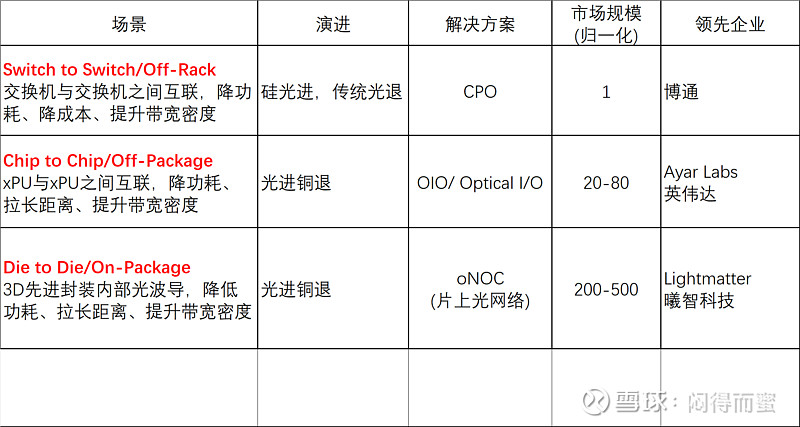

从目前学术界和产业界已经形成共识的情况看,光最终进入大3D先进封装内部,代替封装里面的厘米级的高速铜缆。整个进程,大概分三步:

Co-packaged Optical

AI集群内部机器与机器之间网络互联,大部分已经光纤化了,产业生态正在从高能耗的可插拔模块向高能效比的CPO升级换代。该方向讲了千万遍,这里就不重复了。

可笑的是,去年AI启动时,A股就是以CPO为主题启动光模块的炒作。现在东方财富、同花顺等软件平台,那些光模块股票,都归在CPO概念下。

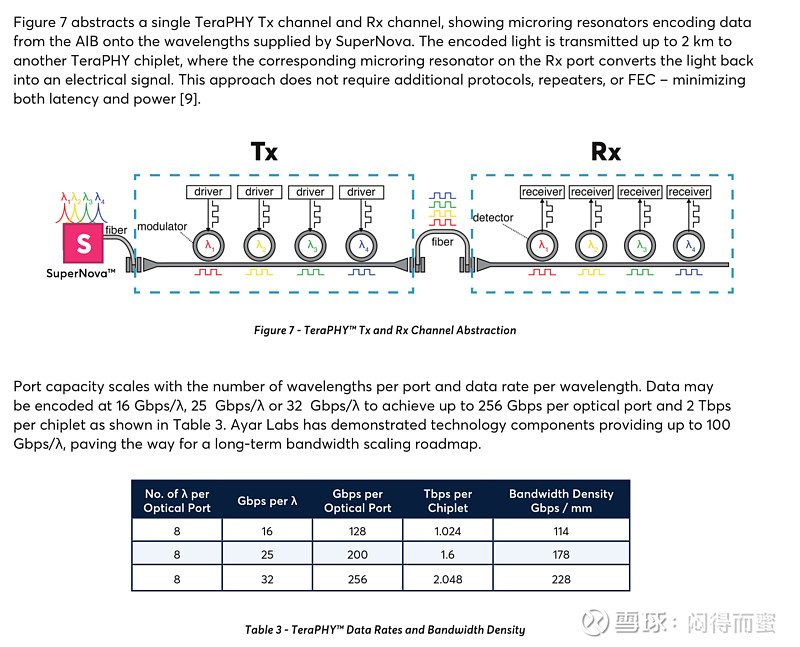

Optical I/O(OIO)

采用密集波分技术,直接将芯片的并行总线延伸到光路通道,舍去了串行化-解串、前向纠错、预加重、均衡等一系列高功耗的电路,并且采用激光器光源外置的方式降低功率密度,大大降低了能耗水平(比铜缆互联降40%以上),互联的距离比铜缆延长2000倍(1m vs 2km)。

Optical IO技术将在2026年H2开始大规模导入,2027年替代数千万跟铜缆,预计在2028年将替代10亿根以上的铜缆线路。

oNOC(片上光网络)

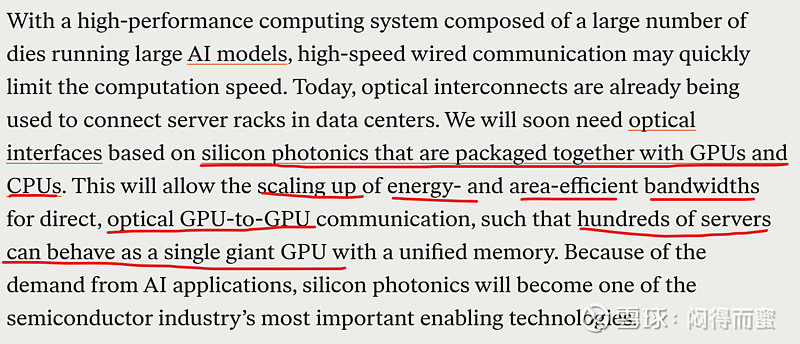

按照台积电董事长今年初在IEEE撰文发布的《How We’ll Reach a 1 Trillion Transistor GPU》链接:网页链接,在2030年之前,将会量产万亿门晶体管的芯片。

虽然半导体工艺持续在演进,但是良率越来越低,投资越来越大,如果所有的功能,都用先进工艺来做,成本奇高无比。3D先进封装的目的,就是把部分运算密集型的电路,用最先进的工艺来做,其他都工艺不敏感的功能,用老一点的工艺,通过异质集成的方法,共封装成一颗大芯片。台积电董事长的观点如下:

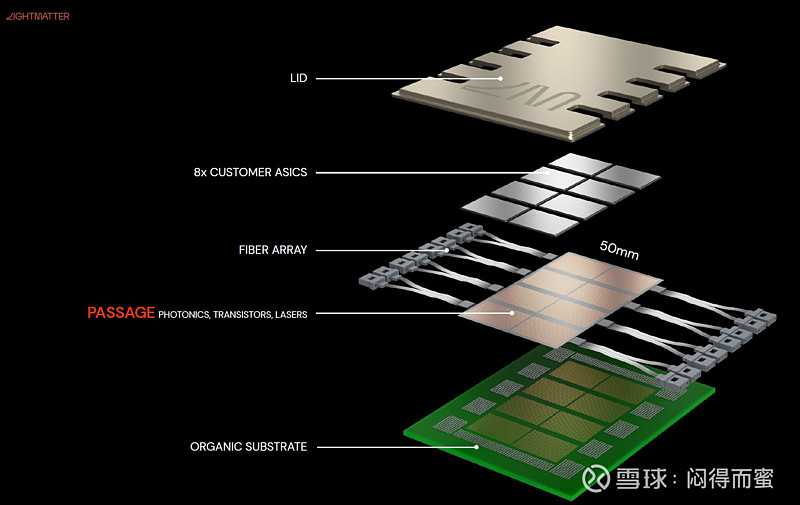

按照学术界的预期,在玻璃基板上大概可以推出40000mm的芯片。这么大的面积,die与die之间的距离超过10cm。因为Die to Die的带宽巨大,继续用铜互联,一方面带宽密度上不去,另外一方面导致功耗能难以承受,必须要用光来进行互联互通才可行。美国Lightmatter和国内的曦智科技(都是MIT同一个实验室出来)这两家前沿布局此目标市场。如图:

这是真正的3D封装,就像盖楼一样,一层封装基板(大型玻璃基板) + 一层光网络层 + 一层几十颗xPU。

投资机遇

1、3D大封装 + 片上光网络,是我国半导体弯道超车的绝佳机遇,看好中芯国际的未来。

2、光电异质集成相关的半导体设备(耦合、键合、封装、测试…),核心标罗博特科;

2、玻璃基板及玻璃基光波导技术,当前能见度不高;

结论

AI集群互联的全光化、光进铜退,不是简单的一撮而就,也不是2~3年完成的短期任务,而是十数年的持续升级演进,100米 --> 10米 —> 5米 —> 2米 —> 1米 —> 0.1米 —> 0.01米,随着技术进步和性价比提升,一步步渗透。

旭日东升,光耀万里。

$罗博特科(SZ300757)$ $半导体ETF(S

本文作者可以追加内容哦 !