台积电第一代1.6 Tbps硅光子和CPO产品有望于2025年量产

原创 深芯盟产业研究部 半导体产业研究 2025年01月02日 08:01 广东

据台湾《经济日报》报道,台积电硅光(SiPh)和光电合封(CPO)技术战略取得重大进展,近日成功实现CPO与先进半导体封装技术的集成。台积电与博通合作,在3nm工艺上调试成功CPO关键技术——微环调制器(MRM),预计2025年初可以交付样品,有望在2025年下半年量产1.6Tbps光电器件。这将开启CPO与高性能计算(HPC)和AI ASIC芯片的集成之路,实现计算从电信号传输到光信号的重大飞跃。预计博通和英伟达将成为台积电首批采用这种光电共封技术的客户。

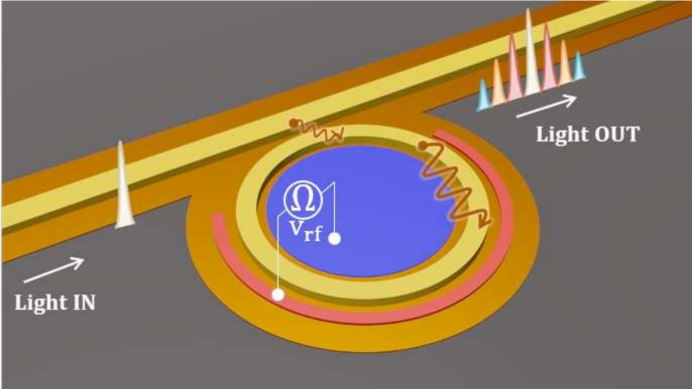

上图是微环调制器(MRM)示意图,显示单频光输入经过调制获得一系列边带光输出。

《经济日报》进一步援引业内消息人士的话称,英伟达计划从GB300芯片开始采用这种CPO技术,随后的Rubin架构也将集成光电模块,希望由此提高通信质量并减轻 HPC 应用中的信号干扰和过热问题,解决当前NVLink 72互连(最多连接72个GB200芯片)的局限性。

硅光和CPO将成为新一代HPC/AI应用的突破性技术

随着AI热潮推动高性能计算(HPC)需求,SiPh和CPO有望突破摩尔定律的局限,成为未来HPC和AI应用的突破性技术平台。SiPh将电子和光子通过先进封装集成到同一芯片中,信号可以通过光波导传输。在硅芯片中集成光波导元件可以同时处理电信号和光信号,不但能够成倍提高处理器内核之间的数据传输速度,而且可以缩小芯片尺寸,降低功耗和生产成本。

除了HPC和AI应用外,光子元件也是激光雷达和医疗传感器的理想选择。

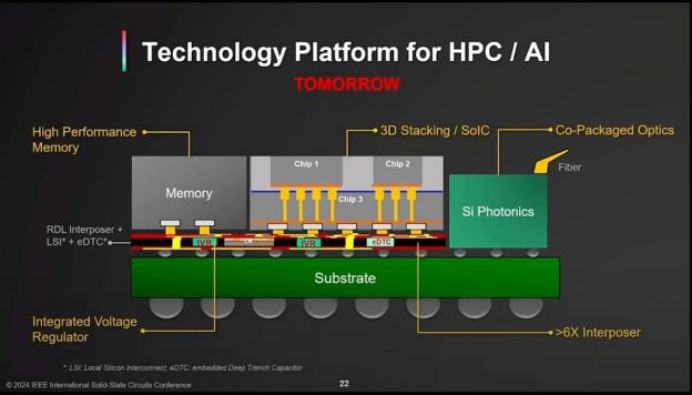

新一代HPC/AI技术平台将通过先进封装集成逻辑芯片、存储器和硅光器件。

AI应用和高性能计算对芯片数据传输与运算速度的需求大幅提升,英特尔与台积电都在力推硅光子应用,因为其高带宽、低功耗、传输范围广、节省成本等优势,有望成为解决AI能效与算力挑战的有效方案。

台湾工研院产学研国际战略中心指出,AI与高端数据中心将是硅光子市场爆发的突破点,预期该技术将从光收发器演进至CPO 和Optical I/O。预估2022年至2027年全球SiPh裸片市场年复合增长率高达48.2%,异质集成与先进封装的实现将成为技术发展重点,但需要更多创新材料。

然而,SiPh仍有许多技术障碍尚未克服。早在10多年前,英特尔就已经将SiPh视为推进封装技术的关键,但到目前尚未实现商业化量产。台积电与多家业界合作伙伴成立硅光子产业联盟,基于其COmpact Universal Photonic Engine (COUPE)技术的SiPh产品有望在2025年实现量产。

TSMC COUPE

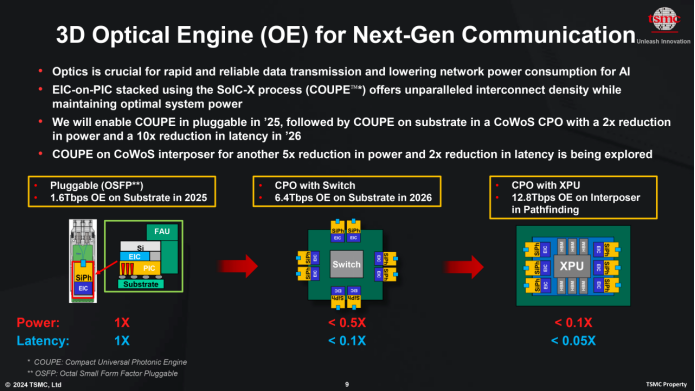

为应对 AI 热潮带来的数据传输量激增需求,台积电着手开发紧凑型通用光子引擎 (COUPE) 技术。COUPE采用SoIC-X芯片堆叠技术,将电子芯片堆叠在光子芯片之上,从而降低芯片间连接的阻抗,并提高能源效率,其效果优于传统堆叠方法。台积电计划在2025年在小型可插拔器件上验证COUPE,随后在2026 年将其以CPO形式集成到 CoWoS 封装中,将光学连接直接引入芯片封装中。

台积电与日月光和富士康等大厂联合成立了SiPh联盟,以推动硅光技术标准协议,整合上下游资源,共同推动台湾加速SiPh产业发展。据悉,Google是采用SiPh技术最积极的云服务商(CSP)之一,已开始部署800G SiPh收发器。

TSMC针对新一代网络通信的3D光学引擎发展规划

台积电第一代3D光学引擎 (COUPE) 将集成到运行速度为1.6 Tbps的OSFP可插拔基板上,这一传输速率已经远超当前铜缆以太网标准(最高800 Gbps),凸显了光学互连对于网络密集型计算集群的直接带宽优势,更不用说预期的节能效果了。看来TSMC的硅光技术开发进度比原计划还要快。

展望未来,第二代 COUPE 将以CPO形式集成到 CoWoS 封装中。与第一代相比,此版本的COUPE 将支持高达 6.40 Tbps 的数据传输速率,且延迟更低。

台积电第三代 COUPE(COUPE集成在CoWoS中介层上)预计将更进一步,将传输速率提高到 12.8 Tbps,同时使光学连接更接近处理器本身。目前,COUPE-on-CoWoS 正处于探索阶段,台积电尚未设定目标日期。

本文作者可以追加内容哦 !