来源:内容编译自IEEE,谢谢。

人们期待已久的新兴计算机网络组件可能终于迎来了它的时代。在上周于圣何塞举行的Nvidia GTC活动上,该公司宣布将生产一种光纤网络交换机,旨在大幅降低 AI数据中心的功耗。该系统称为共封装光学器件(CPO)交换机,每秒可将数十兆比特的数据从一个机架中的计算机路由到另一个机架中的计算机。

如今,在数据中心中,计算机机架中的网络交换机由专用芯片组成,这些芯片通过电气方式与插入系统的光收发器相连(机架内的连接是电气的,但有几家初创公司希望改变这一现状)。可插拔收发器结合了激光器、光电路、数字信号处理器和其他电子设备。它们与交换机建立电气连接,并在交换机端的电子比特和沿光纤穿过数据中心的光子之间转换数据。

共封装光学器件是一种通过将光/电数据转换尽可能靠近交换芯片来提高带宽并降低功耗的方法。这简化了设置,并通过减少所需的独立组件数量和电子信号必须传输的距离来节省电力。先进的封装技术使芯片制造商能够用多个硅光收发器芯片包围网络芯片。光纤直接连接到封装上。因此,除激光器外,所有组件都集成到一个封装中,激光器保持外部,因为它们是使用非硅材料和技术制造的。(即便如此,CPO 只需要 Nvidia 硬件中每八个数据链路一个激光器。)

共封光学:很强,很难

尽管这项技术看起来很有吸引力,但其经济性阻碍了它的部署。“我们一直在等待 CPO,”加州大学圣巴巴拉分校的联合封装光学专家、IEEE 研究员Clint Schow说,他已经研究这项技术 20 年了。谈到 Nvidia 对这项技术的认可,他表示该公司“除非到了 [GPU 密集型数据中心] 无法承担电力成本的时候,否则不会这么做。”因为其所涉及的工程非常复杂,Schow 认为除非“旧方法被打破”,否则它是不值得的。

Omdia 数据中心计算和网络专家 Manoj Sukumaran 对此举充满热情,称其为“真正的大事”。他告诉我们,共封装光学器件是一项“酝酿已久”的技术。该技术、供应商和标准分散在各个小公司及其定制解决方案中。

“这项技术没有标准化,因此即使在超大规模 CSP 中也没有得到广泛采用。

IDC EMEA 高级研究总监 Andy Buss表示,即便是今天,10G 以太网对于铜 RJ45 连接来说,每个端口的功耗仍然很高,而当我们以高数据速率使用当前的光收发器和可插拔模块时,每个模块的功耗是显而易见的——而且随着所需的网络连接数量的增加,每个模块的功耗会迅速增加,成为一个重要的耗电设备。每个收发器的功耗可能在 20W 到 40W 之间,所以这不是微不足道的——而且这不仅需要供电,还需要冷却。

事实上,Nvidia 也将即将到来的 AI 数据中心的功耗作为其动机。Nvidia超大规模和高性能计算副总裁Ian Buck表示,可插拔光学器件消耗了 AI 数据中心“总 GPU 功耗的 10%” 。在一个拥有 40 万个 GPU 的工厂中,这相当于 40 兆瓦,其中一半以上仅用于为可插拔光学收发器中的激光器供电。“拥有 40 万个 GPU 的 AI 超级计算机实际上需要 24 兆瓦的激光器,”他说。

Jensen 在他的主题演讲中强调了这一点。该公司声称功耗降低了 70%,从 1.6T 可插拔收发器的 30W 降低到每个 1.6T CPO 端口仅 9W。Nvidia的 CPO 基于新的微环调制器 (MRM),可额外提高功率效率。

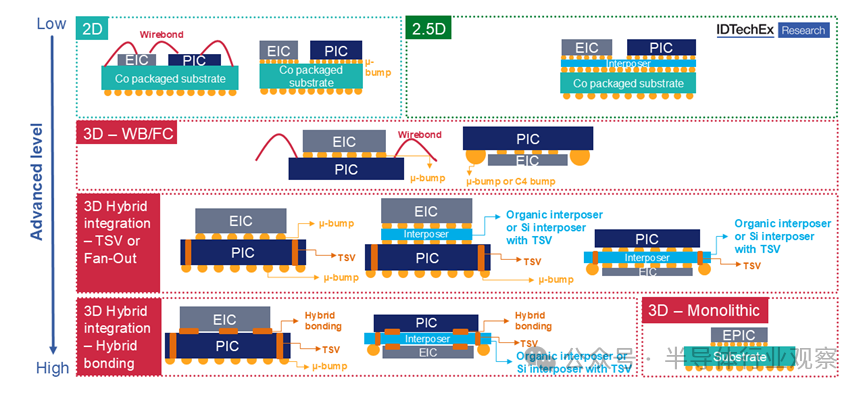

不过,正如IDTechEx 所说,异构集成是共封装光学器件 (CPO) 的关键,它使光学引擎 (OE)(包括光子 IC (PIC) 和电子 IC (EIC))与开关 ASIC 或 XPU 集成在单个封装基板上。CPO 的封装方法通常分为两种:一种涉及光学引擎本身的封装,另一种侧重于光学引擎与 ASIC 或 XPU 等 IC 的系统级集成。这两种方法都需要使用先进的 2.5D 和 3D 半导体封装技术。

光子和电子元件的集成可以通过多种方法实现,每种方法都有不同的优点,也面临着特定的挑战。

2D 集成涉及将 PIC 和 EIC 并排放置在印刷电路板 (PCB) 上,并通过引线键合或倒装芯片技术进行连接。这种方法的优点是封装技术简单、复杂度低、成本效益高。然而,缺点包括显著的寄生电感,这会导致信号完整性问题和高能耗。此外,由于间距限制和对单边连接的依赖,整体 I/O 功能被重组。总体而言,虽然 2D 集成相对容易封装,但使用引线键合会限制收发器带宽并增加能耗,使其不太适合高性能应用。

2.5D 集成通过将 EIC 和 PIC 安装到配备硅通孔 (TSV) 的无源中介层上,提供了一种折中方案。该方法通过使用微凸块或铜柱来减少 EIC 和 PIC 之间的封装寄生效应,从而实现更高的 I/O 连接并实现更精细的布线以增加带宽。此外,中介层的使用允许加入波导层,这可以增强光信号重新分配并支持更好的信号完整性。然而,这种方法也带来了一系列挑战。与 2D 集成相比,2.5D 集成的开发和制造成本更高。此外,虽然 2.5D 集成在 2D 集成的基础上有所改进,但它的寄生效应仍然高于 3D 集成,这会影响整体性能。

3D 混合集成采用更先进的方法,使用先进的半导体封装技术(例如硅通孔 (TSV)、高密度扇出、Cu-Cu 混合键合或有源光子中介层(使用 PIC 作为中介层,如图所示))将 EIC 堆叠在 PIC 之上。通常,3D 集成方法可显著减少寄生效应并支持密集间距配置,从而提高性能。然而,管理散热是一项挑战,因为来自 EIC 的热量会影响 PIC,因此需要先进的热管理解决方案。

在这些不同的封装方法中,硅通孔 (TSV) 技术因其在电力传输和通信效率方面的优势而被视为集成 EIC 和 PIC 的关键技术之一。TSV 可最大限度地降低电压降和电感,为关键组件提供可靠电力,同时缩短互连距离以改善通信。尽管由于硅的介电特性,高频下存在信号完整性挑战,但 TSV 更光滑的金属表面有助于减轻趋肤效应,使其成为高级 EIC/PIC 集成的理想选择。据思科称,其第三代光学引擎采用了 3D TSV(硅通孔)先进封装技术。TSV 的使用解决了电源完整性瓶颈问题,该瓶颈是由向高频工作的 PIC 上的有源器件有效传输电力的挑战以及 EIC 中有源器件数量的增加而引起的。

3D Cu-Cu 混合键合技术可支持个位数微米范围内的凸块间距,正成为最小化 EIC/PIC 接口寄生效应的关键解决方案。该技术已用于高端处理器,通过减少寄生效应提供显著优势,从而降低功耗并提高性能。台积电通过其 SoIC 技术(品牌为 COUPE)推进这一方法,用于堆叠 EIC 和 PIC,旨在利用混合键合实现卓越的集成效率和性能。

3D 单片集成是最先进的技术,目前仍在开发中,它涉及将光子元件嵌入现有电子工艺节点,而改动极小。这种方法将有源光子和电子元件集成在同一芯片中,通过消除对接口焊盘和凸块的需求,减少了寄生效应并简化了封装。然而,它通常依赖于较旧的 CMOS 工艺节点,这可能导致光子性能不佳和能耗较高。尽管存在这些限制,3D 单片集成仍可减少阻抗失配并简化封装。

随着共封装光学器件 (CPO) 成为高端数据中心的关键解决方案,封装技术的选择仍在积极讨论和研究中。每种集成方法都有独特的优势和挑战,不仅要考虑光学引擎的封装,还要考虑涉及 IC(交换机 ASIC/XPU)和光学引擎共同设计的综合系统集成。

英伟达的解决方案:真正疯狂的技术

在主题演讲中,黄仁勋表示:“将 GPU 扩展到数十万个的挑战在于横向扩展的连接。当数据中心现在有体育场那么大时,我们需要一些[新]东西 - 而这正是硅光子学的用武之地。”

他补充道:“硅光子学的挑战在于收发器消耗大量能源。我们宣布推出 Nvidia 首款共封装 [光学] 硅光子系统。

“这是世界上第一个 1.6 Tb/s CPO,基于一种称为微环调制器 (MRM) 的技术。它完全采用台积电这种令人难以置信的工艺技术制造而成。”

黄仁勋将这一进展描述为“真正疯狂的技术”,并将通常用于通过网络交换机连接 GPU 的传统 Mach-Zehnder 可插拔收发器与 Nvidia 的最新进展进行了比较。

他指出,如今每个 GPU 都需要六个独立的收发器,这意味着每个 GPU 的功耗为 180 瓦,成本为 6000 美元。“问题是:我们现在如何扩展到数百万个 GPU?”首席执行官说。“因为如果我们有 100 万个 GPU,我们需要 600 万个收发器,消耗 180 兆瓦。”

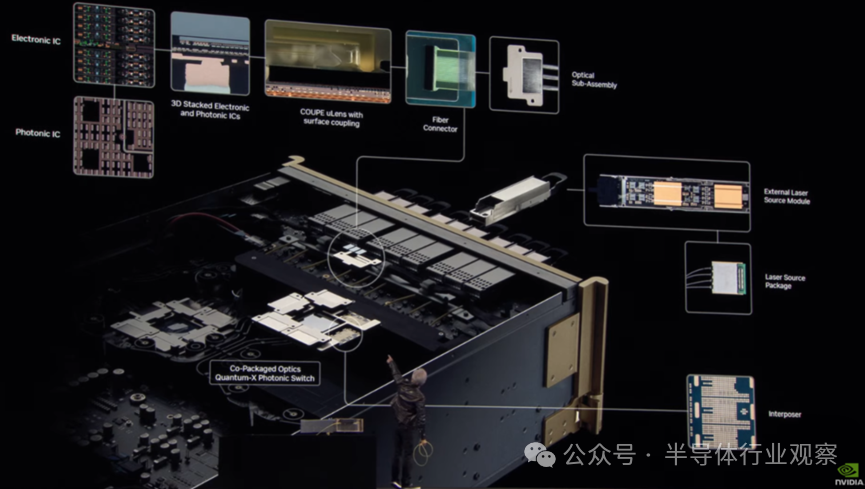

下图显示了所涉及的许多其他组件的概览,首先是台积电制造的电子和光子 IC,并以 3D 堆栈组装。台积电的紧凑型通用光子引擎 (COUPE) 技术包括一个用于表面耦合到光纤阵列的微透镜。在 Quantum-X Photonic 平台的情况下,光学引擎组件通过中介层连接到交换机 ASIC。

如下图所示,Nvidia 的CPO 合作伙伴名单包括 Browave、Coherent、Corning、Fabrinet、Foxconn、Lumentum、Senko、SPIL、Sumitomo、TFC 和台积电。当中,他们还深入介绍了与台积电的合作。

在一段视频,英伟达介绍了台积电制造的“Quantum-X”封装如何结合 18 个硅光子引擎,通过 36 个激光输入实现 324 个光连接和 288 个数据链路。

六个可拆卸光学子组件连接到封装,每个子组件包含三个硅光引擎,可提供 4.8 Tb/s 的总数据量。每个硅光引擎都具有一个 200 Gb/s MRM,采用台积电的“ COUPE ”(紧凑型通用光子引擎)工艺制造,该工艺在 1000 个光子集成电路 (PIC) 上堆叠了 2.2 亿个晶体管。

总体而言,与传统的可插拔收发器方法相比,该方法可将功耗降低 3.5 倍。

黄仁勋在谈到这一进展时表示:“这简直是一个技术奇迹”,并补充说,Nvidia 将在今年下半年开始出货硅光子交换机,随后在 2026 年下半年推出 Spectrum-X 产品。

他补充说,借助英伟达过去五年来一直致力于研发的硅光子技术,数据中心可以节省“数十兆瓦”的电力消耗。

Lumentum 为新交换机提供激光器,该公司云和网络技术业务总裁 Wupen Yuen 评论道:“大幅降低网络功耗的创新将扩大光子元件市场,支持更大的人工智能安装,并加速从铜到光子互连的过渡。”

Coherent 首席执行官 Jim Anderson 在自己的公告中补充道:“我们很高兴能成为 Nvidia 在这种新型收发器方面的合作伙伴。我们预计 CPO 将进一步加速数据中心光纤网络的扩展。”

Nvidia 网络高级副总裁 Gilad Shainer 表示,Nvidia 与 Lumentum 和 Coherent 在激光器和硅光子学方面的合作将实现下一代“百万级人工智能”。

“通过将硅光子学直接集成到交换机中,Nvidia 打破了超大规模和企业网络的旧限制,并打开了百万 GPU AI 工厂的大门。”

Nvidia 表示,在新的 AI 数据中心采用 CPO 交换机将使激光器数量减少四分之一,数据传输的功率效率提高3.5 倍,使信号从一台计算机准时传输到另一台计算机的可靠性提高 63 倍,使网络抵御中断的能力提高 10 倍,并允许客户以更快 30% 的速度部署新的数据中心硬件。

该公司计划推出两类交换机,Spectrum-X 和 Quantum-X。Quantum-X 将于今年晚些时候上市,它基于Infiniband网络技术,这是一种更面向高性能计算的网络方案。它从 144 个端口中的每一个端口提供 800 Gb/s 的速度,它的两个 CPO 芯片采用液冷而不是风冷,越来越多的新 AI 数据中心也采用这种冷却方式。网络ASIC包括 Nvidia 的SHARP FP8技术,该技术允许 CPU 和 GPU 将某些任务卸载到网络芯片上。

Spectrum-X 是一款基于以太网的交换机,可通过总共 128 或 512 个端口提供约 100 Tb/s 的总带宽,并通过 512 或 2048 个端口提供 400 Tb/s 的总带宽。预计硬件制造商将在 2026 年准备好 Spectrum-X 交换机。

Nvidia 多年来一直致力于基础光子技术的研究。但它需要与台积电、康宁和富士康等 11 家合作伙伴合作,才能将这项技术推向商业化阶段。

Nvidia 光学互连产品总监 Ashkan Seyedi 强调,这些合作伙伴带来的技术必须共同优化以满足 AI 数据中心的需求,而不是简单地从这些合作伙伴现有的技术中组装起来。

“CPO 带来的创新和节能效果与你的封装方案、封装合作伙伴和封装流程密切相关,”Seyedi 说道。“创新之处不仅仅在于光学元件本身,还在于它们如何以高产、可测试的方式进行封装,从而让你能够以合理的成本进行管理。”

测试尤为重要,因为该系统集成了许多昂贵的组件。例如,Quantum-X 系统的两个 CPO 中各有 18 个硅光子芯片。每个芯片都必须连接到两个激光器和 16 根光纤。Seyedi 表示,团队必须开发几种新的测试程序才能确保测试正确,并追踪错误出现的位置。

Nvidia 并不是唯一一家推出采用同封装光学器件的网络交换机的公司。博通也是当中一个重要玩家。

光调制器:英伟达和博通的根本区别

Micas Networks本周宣布推出 51.2T 产品,该产品基于 Broadcom 的 51.2 Tbps Bailly CPO 交换机平台,提供 128 个 400G 以太网端口。

Broadcom 的 CPO 提供了 50% 的功耗降低(通过移除 DSP),但它基于 Mach-Zehnder 调制器 (MZM)——光收发器中的标准组件。

博通光学系统部门产品营销高级经理罗伯特·汉娜 (Robert Hannah)解释说,博通为其Bailly CPO 交换机选择了更为成熟的 Mach-Zender 调制器,部分原因是它是一种更为标准化的技术,可能更容易与现有的可插拔收发器基础设施集成。

Micas 的系统使用单个 CPO 组件,该组件由 Broadcom 的Tomahawk 5 以太网交换机芯片和八个 6.4 Tb/s 硅光子光学引擎组成。该风冷硬件现已全面投入生产,领先于 Nvidia 的 CPO 交换机。

汉娜称 Nvidia 的参与是对 Micas 和博通时机的认可。“几年前,我们决定滑向冰球将要到达的地方,” Micas 首席运营官米奇·加尔布雷斯(Mitch Galbraith) 表示。他说,随着数据中心运营商争相为其基础设施提供动力,CPO 的时代似乎已经到来。

与使用标准可插拔收发器的系统相比,这款新交换机有望节省 40% 的功耗。不过, Micas 公司企业战略副总裁Charlie Hou表示,CPO 更高的可靠性同样重要。“链路抖动”是指可插拔光纤链路的瞬时故障,是导致已经非常长的 AI 训练运行时间延长的罪魁祸首之一,他说。CPO 预计链路抖动会更少,因为信号路径中的组件更少,还有其他原因。

如上所述,Broadcom 的方案与 Nvidia 的方案之间的一个根本区别是光调制器技术,该技术将电子比特编码到光束上。硅光子学中主要有两种类型的调制器 - Mach-Zender(Broadcom 所采用的并且是可插拔光学器件的基础)和微环谐振器(Nvidia 所选择的)。在前者中,穿过波导的光被分成两个平行的臂(arm)。然后,每个臂可以通过施加的电场进行调制,从而改变通过的光的相位。然后,这两个臂重新连接形成单个波导。根据两个信号现在是否同相或异相,它们将相互抵消或合并。因此,电子比特可以编码到光上。

微环调制器要紧凑得多。它不是将光沿着两条平行路径分开,而是在光的主路径一侧悬挂一个环形波导。如果光的波长可以在环中形成驻波,它将被抽走,从而将该波长从主波导中过滤掉。究竟哪种波长与环产生共振取决于结构的折射率,而折射率可以通过电子方式进行操控。

然而,微环的紧凑性是有代价的。微环调制器对温度敏感,因此每个调制器都需要内置加热电路,必须小心控制加热电路,而且会消耗电力。另一方面,Mach-Zender 设备要大得多,导致更多的光损失和一些设计问题,Schow 说。

Schow 表示,Nvidia 成功将基于微环的硅光子引擎商业化是“一项了不起的工程壮举”。

未来的 CPO

Schow 表示,大型数据中心希望从 CPO 获得的节能效果主要是一次性的。之后,“我认为这将成为新常态。”不过,电子设备其他功能的改进将使 CPO 制造商能够继续提高带宽——至少在一段时间内。

Schow 怀疑单个硅调制器(在 Nvidia 的光子引擎中以 200 Gb/s 的速度运行)能否超过 400 Gb/s。不过,其他材料(如铌酸锂和磷化铟)应该能够超过这个速度。关键在于以可承受的价格将它们与硅元件集成在一起,圣巴巴拉的OpenLight等团体正在研究这个问题。

与此同时,可插拔光学器件也并非一成不变。本周,博通推出了一款新型数字信号处理器,该处理器可使 1.6 Tb/s 收发器的功耗降低 20% 以上,部分原因在于采用了更先进的硅工艺。

Avicena、Ayar Labs和Lightmatter等初创公司正在努力将光学互连引入 GPU 本身。前两家公司已经开发出可以与 GPU 或其他处理器装入同一封装中的芯片。Lightmatter 更进一步,将硅光子引擎作为未来芯片 3D 堆叠的封装基板。

知名光学分析机构lightcounting在其文章中表示,横向扩展网络是低风险的 CPO 切入点,但纵向扩展光纤互连更为关键。混合专家 (MoE) 模型的快速响应时间需要专家并行性,即跨 GPU 划分专家。Jensen 解释了量和响应时间之间的权衡,他的示例展示了一个最佳点,即需要专家并行 64,这意味着专家被划分到 64 个 GPU 实例中。Blackwell 一代 NVL72 机架使用 NVLink 在无源铜背板(或主干)上创建了一个 72-GPU 纵向扩展域。Nvidia 将在 2H26 中为 Vera Rubin NVL144 使用类似的设计,可能会将无源电缆的数量增加一倍。

Nvidia隐瞒了 Rubin Ultra NVL576 设计的细节,但 Kyber 机架布局显然为 NVLink 互连引入了新的要求。尽管如此,144 个 GPU 封装仍可装入单个机架中,因此最大覆盖范围约为 2 米。路线图省略了 Feynman 预期的 NVLink 规模,但我们相信它将扩展到多个机架,届时将需要光学器件。

Nvidia在 GTC 2022 上首次宣布了通过光纤实现 NVLink 的计划。该公司在内部构建了至少一个这样的集群,但重定时光收发器的高功耗对于广泛部署来说是不可能的。消除 DSP 是向前迈出的一步,但需要为未来的改进开辟道路。这就是 Nvidia 冒险使用 MRM 等新技术的原因。考虑到扩展能力的重要性,该公司可能正在研究广泛的新光学技术。NVLink

CPO 的 2028 年时间表为 Nvidia 提供了两代人在横向扩展网络中证明其技术的机会。这将降低 GPU 不可避免地转向 CPO 的风险,这只是时间问题,而不是是否的问题。

本文作者可以追加内容哦 !