(文/姜羽桐)自初代HBM问世以来,已迅速发展至第六代产品(HBM4),尤以近年来迭代最为剧烈。

数据显示,今年HBM出货量将同比增长70%,需求空前高涨。但不是所有的HBM都会被青睐,在英伟达等算力提供商及相关存储厂商路线计划中,2025年的荣光属于HBM4:SK海力士率先推出12层样品;三星表态下半年生产尖端的HBM4;美光亦或将HBM4的推出时间定在今年。

在抢占市场的诱惑下,尽快制造HBM4变得迫在眉睫。而随着堆叠层数的攀升,HBM4最艰难的部分是要满足JEDEC(固态技术协会)制定的775m厚度标准。传统技术已经很难完成,这要求存储厂商必须慎重地选择路线方案——是无助焊剂键合(Fluxless Bonding),还是混合键合(Hybrid Bonding)?

巨头“捍卫”775 m,16层堆叠艰难重重

2024年,存储产业传来一则消息——“制定HBM4标准的JEDEC(固态技术协会)正商榷打算放宽HBM4封装厚度,由720 m增至775 m。”据说,在那场制定标准的讨论中,SK海力士、三星电子和美光坚持775 m,英伟达、AMD也接受了该建议。

存储三巨头坚决“捍卫”775 m的主要原因是,进入HBM4时代,传统技术已无法在720 m的限制下实现16层堆叠,它们需要争取时间和空间。

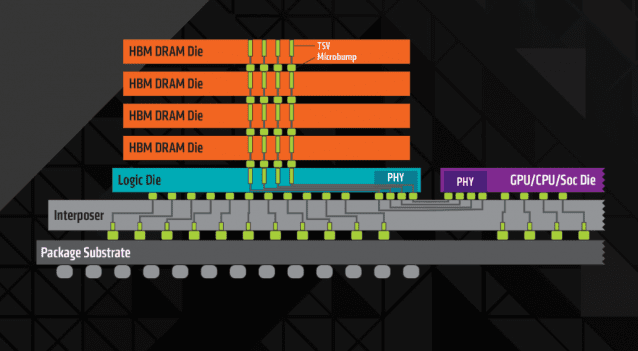

过去,HBM通常利用TSV、微凸点和热压键合技术实现多层DRAM颗粒的垂直堆叠与互连以制备存储器芯片,各大存储厂商的办法略有不同——SK海力士采用MR-MUF技术,该技术在每次堆叠DRAM时,会通过加热进行临时连接,最终在堆叠完成后进行一次回流焊以完成键合,随后填充环氧树脂模塑料(EMC),使其均匀渗透到芯片间隙;三星电子、美光则使用TC-NCF技术,在各层DRAM之间嵌入NCF(一种非导电胶膜),并通过热压键合(TCB)从上至下施加热量和压力,NCF在高温下熔融,起到连接凸点并固定芯片的作用。

图片 / HBM内部结构

想要控制封装厚度,从物理角度讲有两个办法,一是基于现有的互联技术,将每个DRAM层磨薄,但不可靠;二是从DRAM层与层之间从互联的填充物方面下手。传统倒装芯片键合中,通常使用助焊剂清理DRAM Die表面氧化层,保证键合过程中机械和电气连接不会受到氧化层影响。但是,残留的助焊剂又将扩大各Die之间的间隙,因此成为摆在工程师面前一道严峻的问题。

集微网向提供先进封装设计、测试开发等技术服务(解决方案)的普赛微科技征询,COO喻涛介绍:“随着HBM的迭代,微凸点间距通常在40m以下,这对助焊剂清洗带来不小的挑战。助焊剂的残留可能与触点处的锡帽(Solder Cap)发生化学反应,并在塑封料填充时产生缺陷对后道组装工艺产生不确定因素。”残留物还将引发堆叠间隙增大、热应力集中等问题。

特殊节点的召唤,无助焊剂键合登场

当助焊剂的缺点在先进封装工艺中变得越来越明显,开始妨碍半导体公司“赚钱”时,无助焊剂键合技术便得到存储厂商青睐。就目前而言,该技术在HBM,尤其HBM4封装过程中具有无可比拟的三大优势:

一、无助焊剂键合技术可有效缓解大尺寸、微凸点节距芯片的助焊剂残留问题,提高产品的长期可靠性;

二、热压键合时,易挥发的助焊剂在高温下会形成蒸汽,进而污染镜头,将严重影响对位精度。而无助焊剂键合技术可减小工艺过程对机台镜头的影响,提升对位精度;

三、缩小堆叠芯片之间的间隙,增加堆叠层数,缩小堆栈的整体厚度。

无助焊剂键合技术的优点固然多,但喻涛认为,从未来技术发展趋势来看,该技术亦存在较大局限性:一方面,HBM4接口宽度从每堆栈1024位增加到每堆栈2048位,接口的大小和间距进一步缩小到m级别,从键合密度上看目前无助焊剂键合技术难以满足高密度互连需求;另一方面,热压键合技术依靠微凸点实现芯片的片间键合,芯片间需要预留30~40m的高度以确保NCF或MUF/CUF等底填料的填充,这仍将导致堆栈的总厚度急剧上升,难以实现更高层数的堆叠。

这并未阻挡存储三巨头对无助焊剂键合技术应用于HBM4的极大热情。去年11月就有韩国媒体指出,三星电子、SK海力士、美光均对在下代HBM4内存中采用无助焊剂键合技术感兴趣,正进行技术准备。美光在与合作伙伴测试工艺方面最为积极,SK海力士考虑导入,三星电子也保持密切关注。

但由于存储厂商在传统HBM芯片键合技术上的区别,无助焊剂键合技术尚需谨慎评估。此外,无焊剂还是一种主要应用于MR-MUF的技术,这对于使用TC-NCF技术的玩家不够友好,它们需要改变整个设备基础设施才能实现。据了解,无助焊剂键合设备主要包括热压键合机、共晶键合机、激光辅助键合机等。目前国外厂商占据大部分市场份额,包括K&S、ASMPT、SET、PALOMAR等;国内设备厂商虽然有不错的进展,但仍存在差距。

存储巨头态度微妙,混合键合暂“搁置”

作为HBM键合技术强有力的“竞争者”,无助焊剂键合技术虽然暂时解决了存储厂商面对16层HBM4这一重要节点的忧虑,并进入“评估阶段”,但其命运可以用两句话形容——过去用不到,今后用不着。未来随着HBM产品堆叠层数越来越高,甚至攀升到20层及以上,无助焊剂键合技术必然要走下舞台。

事实上,三大存储厂商并未将所有的希望寄托在无助焊剂键合技术上,它们还在做另一手准备。IEEE第74届电子元件和技术会议上,三星就在发表的《用于HBM堆叠的D2W铜键合技术研究》论文中强调,“16个堆栈及以上的HBM使用混合键合是必须的”。

图源 / TechInsights

在HBM领域,混合键合被认为是“梦想技术”,甚至称为自EUV以来半导体制造最具变革性的创新,其通过两个芯片覆盖介电材料如二氧化硅,介电材料嵌入与芯片相连的铜接点,接着将两芯片接点面对合,再透过热处理让两芯片铜接点受热膨胀对接。与已广泛使用的微凸块堆叠技术相比,混合键合由于不配置凸块,可容纳较多堆叠层数,也能容纳较厚的晶粒厚度,以改善翘曲问题。此外,使用混合键合的芯片传输速度较快,散热效果也较好。

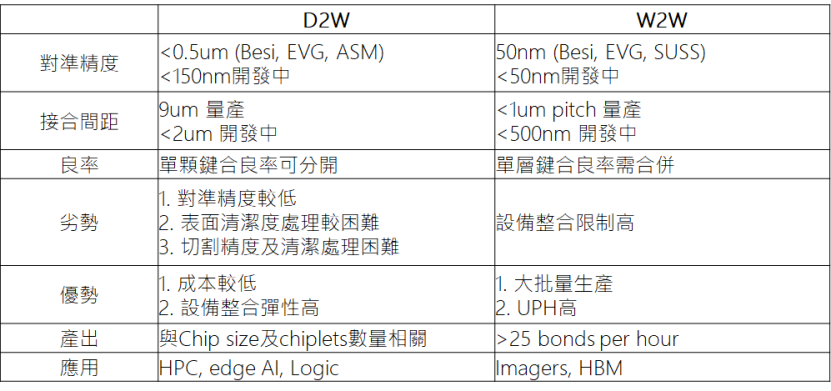

作为存储厂商重点开发的技术,混合键合分为晶圆对晶圆(Wafer-to-Wafer,W2W),和芯片对晶圆(Die-to-Wafer,D2W),两种方案具有不同的优缺点。

芯睿科技董事长周玮向集微网介绍:“D2W较多应用在HPC、edge AI、Logic领域,接合间距<10 m,优点是成本较低、设备整合弹性高,缺点是对准精度较低、表面清洁度处理较困难、切割精度及清洁处理困难;W2W较多应用在HBM、Imager领域,对准精度<50nm,接合间距<1 m,优点是可以大批量生产、UPH高,缺点是设备整合限制高。”他表示,就HBM而言,如果良率够高,W2W方案是最简单的。

需要特别指出的是,尽管混合键合因诸多优势而被业界寄予厚望,但还有诸多工作要做,这也是被存储厂商暂缓“出道”的原因。譬如,成品裸晶的良率问题,键合界面需要超高平整度对封装制程的考验,以及混合键合制程需要ISO3以上的洁净等级,均将大幅增加传统封测厂成本。Brewer Science首席应用工程师Alice Guerrero曾表示:“要成功地将混合键合进行大批量生产,需要解决与缺陷控制、对准精度、热管理、晶圆翘曲、材料兼容性和工艺量相关的挑战。”显然,混合键合的全面到来尚需时日。

这与存储厂商对混合键合微妙的态度一致,不久的将来它们不得不使用该技术,但目前希望延迟这一昂贵技术的使用,不要立即“上马”HBM4,至少等到HBM4E或HBM5。

先进封装形势大好,键合市场增速显著

摩尔定律行至瓶颈处,先进封装从先进制程手中取得“接力棒”,成为后摩尔时代的主力军,牵动键合设备迎来利好。市调机构TechInsights统计预测,2023年全球半导体封装设备市场规模约为43.45亿美元,其中键合/固晶机市场规模约为10.85亿美元,同比下滑15.43%,价值量占比25%左右。随着先进封装发展,键合机市场规模有望在今年增长至17.48亿美元,增速显著。

在国际上,混合键合设备领域的主要玩家集中在欧洲、北美和日本,包括EVG(欧洲真空技术集团)、SUSS MicroTec、BESI、应用材料、科磊、泛林集团、ASMPT等,它们依托先进的技术牢牢把控着主导权。虽然我国多家设备制造商为进入混合键合领域而努力,但市场需求的先天不足和客户的缺少,使得设备厂商面临较大挑战的同时,混合键合大规模商用也存在难点。从实际运用看,尽管台积电、英特尔和三星都是混合键合技术的拥趸,但台积电却是迄今为止唯一一家将混合键合商业化的芯片公司。

最后,混合键合技术在AI、数据中心等领域具备不可替代性,但短期内还受限于成本和工艺成熟度,尚需进一步推动工艺标准化和生态系统建设。“从短期看,无助焊剂键合在未来5年内仍会是主流技术之一,尤其非尖端领域;从长期看,混合键合将逐步渗透到更多高端应用场景,但需要等待成本下降和产业链成熟。”喻涛对集微网表示。

对于16层HBM4和16层HBM4E,市调机构TechInsights判断,因混合键合未较微凸块具明显优势,尚无法断定哪一种技术能受青睐……但是,三大存储厂考量堆叠高度限制、IO密度、散热等要求,已确定于20层堆叠的HBM5使用混合键合。

以2025年为节点,存储厂商正不断加码混合键合技术,设备厂商亦持续投入混合键合研发,混合键合在HBM产品中的制造可行性已取得显著提升。3年后,随着HBM5的正式推出,混合键合将成为下一代技术的必然选择。而HBM,也将更加昂贵。

本文作者可以追加内容哦 !